《TAIPEI TIMES》Apple to use updated TSMC technology

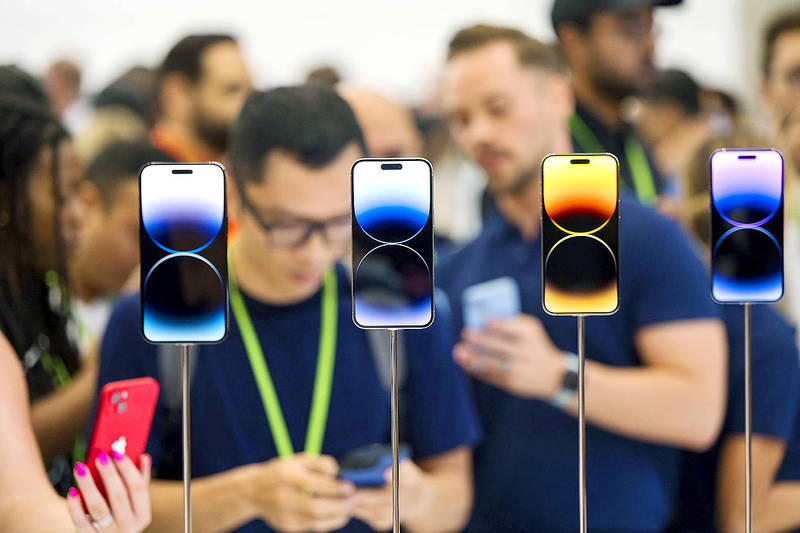

Apple iPhone 14s are displayed at an event at the Apple Park campus in Cupertino, California, on Wednesday last week. Photo: Bloomberg

PREMIUM IPHONES: ‘Nikkei Asia’ reported that TSMC’s A17 mobile would be mass produced using N3E and is expected to be available in the second half of next year

Staff writer, with CNA and Reuters

Apple Inc is planning to use an updated version of Taiwan Semiconductor Manufacturing Co’s (TSMC, 台積電) latest chip production technology for iPhones and Macbooks next year, the Nikkei Asia reported yesterday.

The A17 mobile processor, which is under development, would be mass produced using TSMC’s 3-nanometer enhanced (N3E) process technology, expected to be available in the second half of next year, the newspaper said, citing people familiar with the matter.

The A17 would be used in the premium model of the iPhone lineup slated for release next year, it said.

Apple declined to comment, while TSMC did not immediately respond to a Reuters request for a comment.

Current iPhone models use the A15 processor, while the iPhone 14 Pro, which was released last week, features the same chip.

TSMC has a 54 percent share in the global market for contractually produced chips, supplying Apple, Qualcomm Inc and other firms.

TSMC said the development of its high-end process has been proceeding smoothly and commercial 3-nanometer production is to start later this year, a year ahead of the launch of N3E.

The 3-nanometer process started a trial run last year, with the firm’s 5-nanometer process the latest to enter mass production.

TSMC’s 3-nanometer family uses FinField-effect-transistor technology, a 3D transistor structure that enables chips to run faster using the same amount of power or to run at the same speed on reduced power.

Late last month, TSMC chief executive officer C.C. Wei (魏哲家) said that the company had encountered many difficulties in developing the 3-nanometer process, but would soon begin mass production with many of its customers keen to work with it.

Meanwhile, TSMC plans to mass produce chips using the more sophisticated 2-nanometer process in 2025 at a wafer plant to be built at the Hsinchu Science Park (新竹科學園區).

The 2-nanometer process would become the first technology in which TSMC employs a gate-all-around structure, which reduces undesirable variability and mobility loss, making the technology the most competitive and efficient on the market.

Wei has touted the company’s 2-nanometer process as the industry’s best and most efficient technology when mass production begins.

新聞來源:TAIPEI TIMES